1. はじめに

積層セラミックコンデンサには、DCバイアスをかけると静電容量が大きく低下してしまうものがある。一般に、温度特性によってDCバイアス特性もおおよそ決まっている。温度特性がCHやC0GのものはDCバイアスに対して容量変化はほとんどなく、B特性やF特性のものは定格電圧までかけると容量が半分以下になってしまう。

例えば、耐圧6.3 V、100 μFの積層セラミックコンデンサを5 Vの電源につけたとき、実際には30 μFくらいの性能しかなかったりする。また、スイッチング回路に使うと、その非線形性から高電圧が発生したりすることがあるようだ1。

今回は、逆に、積層セラミックコンデンサのDCバイアス特性を利用して、VCOを作ってみようと思った。VCOはLC共振のクロスカップル発振回路を使う。

2. 部品さがし

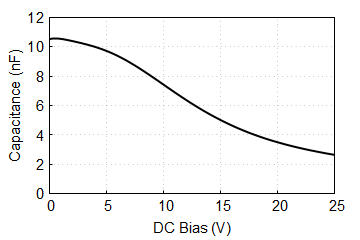

まずは、DCバイアス特性が悪いコンデンサを探した。VCOの発振周波数をできるだけ高くしたいので、容量が小さいものを選びたい。だけど、容量が~nF以下のやつはたいていC0G特性かCH特性なので今回は使えない。また、耐圧が低い方が、容量変化も大きいはず。秋月電子で探していたらいい感じなものを見つけた。

チップ積層セラミックコンデンサー 0.01μF25V B 0603 (50個入): パーツ一般 秋月電子通商-電子部品・ネット通販

チップの積層セラミックコンデンサで、10 nF、耐圧25 V、B特性で50個入りで100円。大きさが0603(0201)なのでかなり小さい。データシートを見るとゼロバイアスで10 nFあるのが、定格の25 Vで2.6 nFまで落ちるので今回の目的においてはかなり優秀だ。容量比で言うとだいたい4くらい。

ちなみに、村田製作所のコンデンサやインダクタはSimSurfingというツールを利用して、部品のデータやSpiceモデルをダウンロードしたりすることができる。おすすめ。 設計支援ソフトウェア SimSurfing | 設計支援ツール | 村田製作所

3. VCOの回路

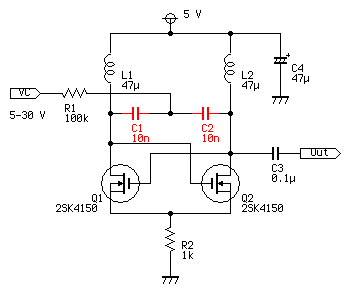

回路図を下に載せた。VCOはふつうのクロスカップル発振回路とした。トランジスタは部品箱にあった2SK4150というMOSFETを使った(これ、大学1年生のときに買ったやつで、ちょっと懐かしい思い出がある2)。図のC1とC2に、上で選んだ積層セラミックコンデンサを使う。

発振周波数はL1, L2とC1, C2の共振で決まり、上の式となる。計算すると、L1=47 µHとC1=10 nFのとき、発振周波数は232 kHzになる。C1とC2の真ん中から100 kΩを通してDCバイアスをかけられるようにした。

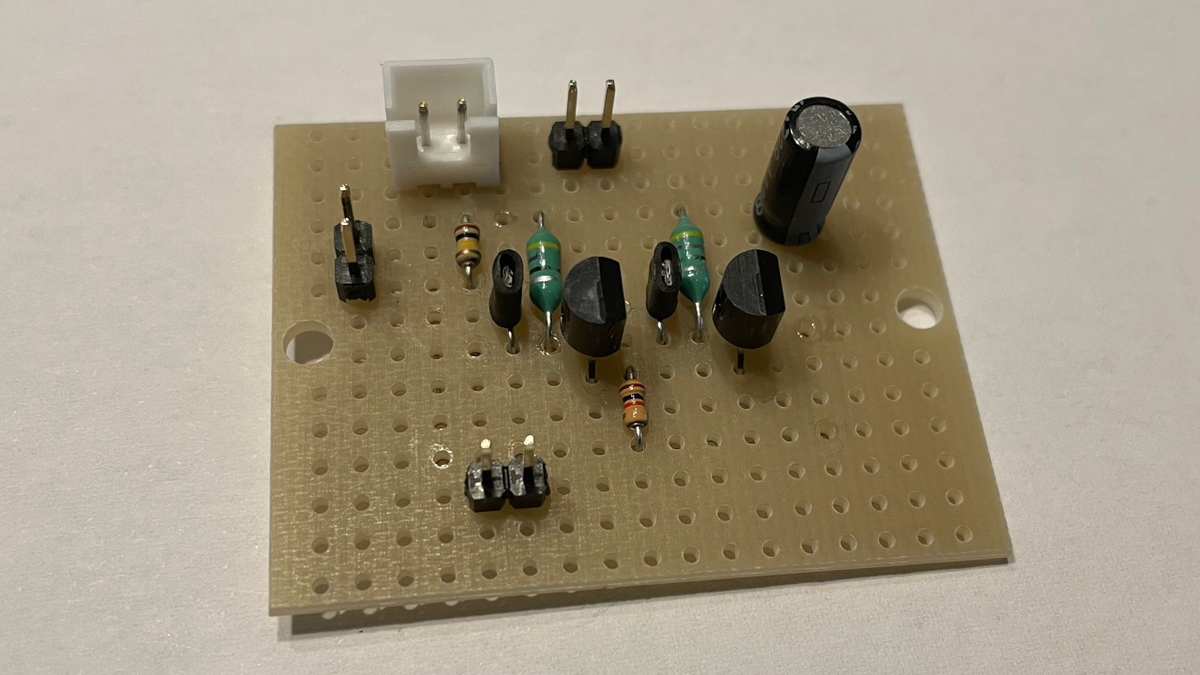

余ってた片面ユニバーサル基板を使った。ちっさいチップコンデンサは、まず小さく切った基板にはんだ付けしたあと、足を2本生やしてリード線タイプのかんじにしてみた。

4. 発振特性の測定

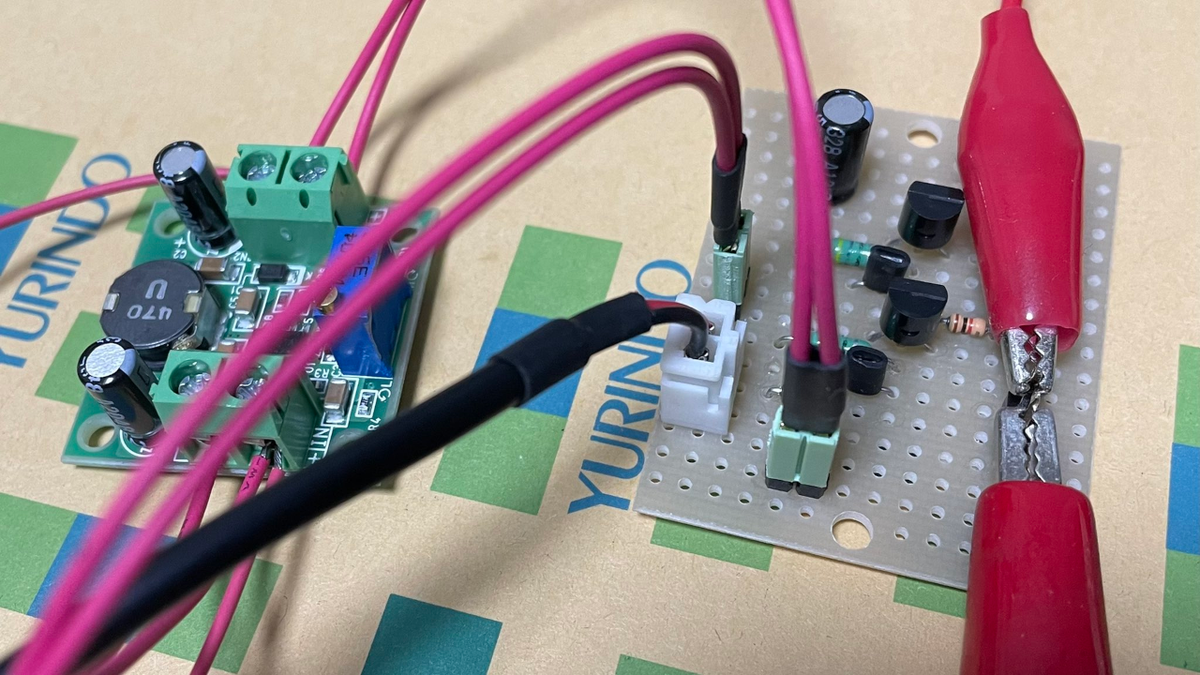

テスターで積層セラミックコンデンサにかかる電圧を測定しながら、もうひとつのテスターで発振周波数を測定した。DCバイアスは秋月電子の昇圧回路キットを用いた。発振周波数は0 Vのとき221 kHzで、27 V(定格25 Vをちょっとオーバー)のとき406 kHzだった。周波数も可変幅も期待通りの結果になったと思う。